复旦大学集成芯片与系统全国重点实验室共有7篇论文入选ISSCC 2025,创历史以来最高,体现了学校在芯片设计领域的持续创新能力。7篇论文研究方向包括:Chiplet 3D集成芯片、AI专用处理器、高速有线互联、模拟电路、无线通信、宽带接收机高线性度低功耗技术研究、无线收发机等。

01

论文一

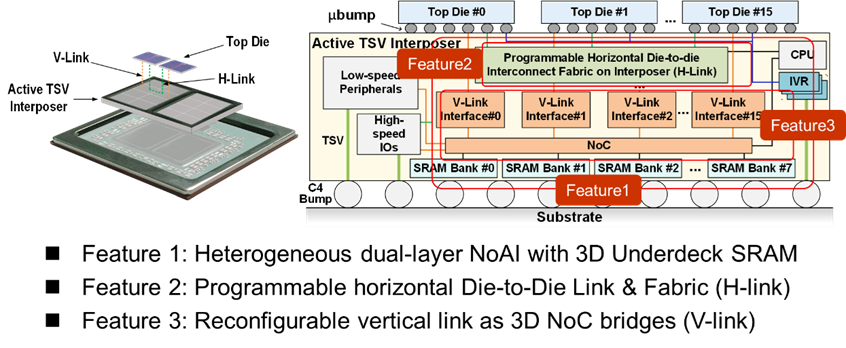

SHINSAI: A 586mm2 Reusable Active TSV Interposer with Programmable Interconnect Fabric and 512Mb 3D Underdeck Memory

陈迟晓副研究员、刘琦教授、刘明院士团队开展封装、架构、EDA、电路的跨层次协同研究,设计了一款可复用的有源硅基板—“芯斋”,并基于芯斋完成了16颗存算一体算力芯粒的三维集成。该工作的主要亮点包括:电路交换与包交换异构的双层硅基板互连网络,集成了512Mb底层SRAM存储;可编程2.5D芯粒间互连链路,可针对不同的芯粒间互连拓扑,实现微凸点(microbump)级细粒度灵活路由;可重构3D垂直链路,桥接顶层芯粒和底层“芯斋”硅基板之间的片上网络,并适配不同的上行/下行带宽。

“芯斋”有源硅基板的整体架构和技术亮点

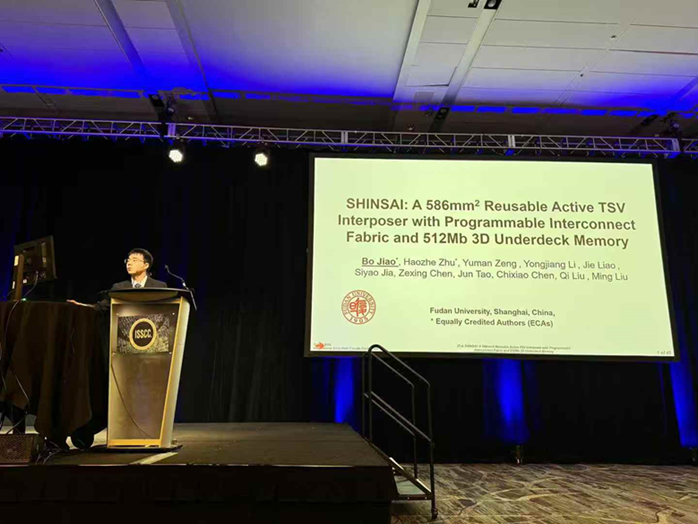

焦博博士生报告论文

相关论文成果以“SHINSAI: A 586mm2 Reusable Active TSV Interposer with Programmable Interconnect Fabric and 512Mb 3D Underdeck Memory”为题,入选第72届ISSCC(国际固态电路会议)。本研究成果是全国重首次在固态电路领域顶会发表三维集成芯片,也是全国少有的集成芯片研究成果入选ISSCC。该文章第一作者为焦博博士研究生和朱浩哲博士后,通讯作者为陈迟晓副研究员。

陈迟晓副研究员、刘琦教授、刘明院士团队参会人员

02

论文二

An 8-to-28GHz 8-Phase Clock Generator Using Dual-Feedback Ring Oscillator in 28nm CMOS

面向下一代超高速有线通信接口电路中高数据传输速率与低时钟抖动的需求,闫娜教授和许灏青年研究员团队提出一种超宽频带覆盖、低相位噪声、高相位精度的八相位时钟产生电路。所提出的双反馈环路环形振荡器,通过解耦频率产生环路和相位同步环路,显著提升了给定工艺节点下环形振荡器的最高振荡频率和工作频带覆盖范围。此外,利用宽带延时锁相环产生的低时钟抖动八相位信号注入锁定环形振荡器,在不恶化相位噪声的基础上,提高了输出相位精度。该工作在8~28GHz八相位时钟信号输出频率下,实现了小于38fs的时钟抖动和小于3度的相位误差,在所有国际上已报道的多相位时钟工作中,该工作实现了最宽工作频带和最小时钟抖动。

田野辰博士生报告论文

该工作以“An 8-to-28GHz 8-Phase Clock Generator Using Dual-Feedback Ring Oscillator in 28nm CMOS”为题,发表于2025年ISSCC的高速有线通信(High Speed Wireline)分会场。该文章第一作者为复旦大学田野辰博士研究生,通讯作者为复旦大学闫娜教授和许灏青年研究员。

03

论文三

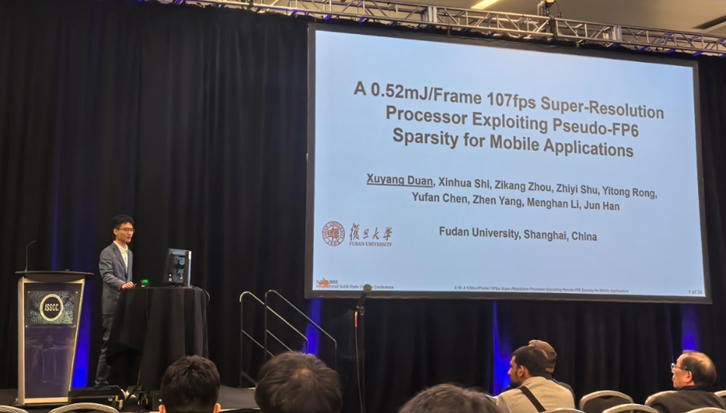

A 0.52mJ/Frame 107fps Super-Resolution Processor Exploiting Pseudo-FP6 Sparsity for Mobile Applications

针对移动端视频应用中高画质、高帧率需求与设备功耗、硬件资源限制之间的矛盾,韩军研究员团队设计了一款具有极高能效的视频超分辨率处理器芯片。首先,针对超分辨率神经网络模型的层融合数据流计算范式的高片上存储需求,该工作提出了行缓存感知的计算存储调度策略,减少了89%的片上存储需求。其次,针对网络模型的高推理精度需求和低数据稀疏性特征,该工作提出了一种新型数据格式来支持高精度推理和跳零计算,减少了64%的推理延迟。最后,针对反卷积算子硬件资源利用率低的难题,该工作提出了一种混合数据流方案,能够在复用卷积算子数据通路的同时提高75%的MAC利用率。在ISSCC会议和JSSC期刊已公开的超分辨率处理器芯片中,该工作实现了最低的单帧推理功耗(0.52mJ/Frame),展现了卓越的能效优势。

段旭阳博士生报告论文

该工作以“A 0.52mJ/Frame 107fps Super-Resolution Processor Exploiting Pseudo-FP6 Sparsity for Mobile Applications” 为题,发表于2025年 ISSCC的处理器(Processors)分会场。该文章第一作者及演讲者为复旦大学段旭阳博士研究生,通讯作者为复旦大学韩军研究员。

04

论文四

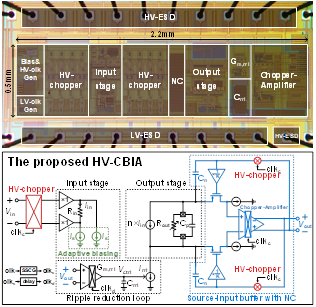

A 36V Current-Balancing Instrumentation Amplifier with ±24V Input Range, 5.6MHz BW, and 140dB CMRR at All Gain Settings

徐佳伟研究员、洪志良教授团队创新性地提出了应用于工业信号采集的高压电流平衡仪表放大器,该项工作通过基于最小电流选择器的自适应偏置技术,将静态电流限制在0.7mA的同时实现了±24V的高输入范围,打破了传统架构对输入范围的限制;针对片外增益调节电阻的寄生电容限制带宽以及低增益模式下噪声密度抬升的问题,采用源极输入缓冲器,将缓冲器引入的噪声降低为原来的50%,同时结合负电容设计,抵消寄生电容,实现了50倍增益下280MHz增益带宽积和0.4倍增益下104nV /√Hz噪声密度;通过浮动电压源控制的高压斩波技术,在8-36V供电电压下将等效输入失调控制在5μV以内,并将共模抑制比提升至140dB以上。该高压电流平衡仪表放大器在输入范围、带宽、能效等方面突破了传统仪表放大器架构的限制,为工业信号采集提供了一种高性能、低功耗的设计思路。

放大器芯片照片和架构框图

该工作以“A 36V Current-Balancing Instrumentation Amplifier with ±24V Input Range, 5.6MHz BW, and 140dB CMRR at All Gain Settings”为题,发表于ISSCC 2025的Amplifiers and Analog Front Ends分会场。该文章由徐佳伟研究员和洪志良教授作为指导老师,第一作者为叶深硕士研究生,并由蒋旻格、王嘉昊等学生协助完成。

叶深硕士生报告论文

徐佳伟研究员、洪志良教授团队参会人员

05

论文五

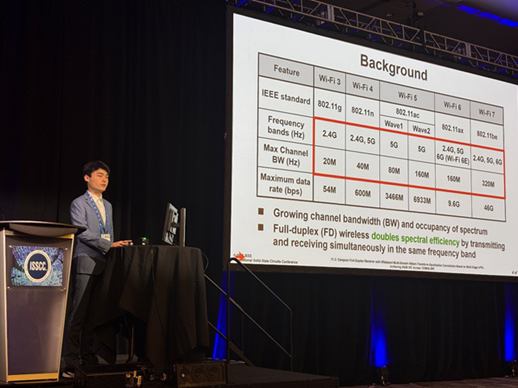

11.3 Compact Full-Duplex Receiver with Wideband Multi-Domain Hilbert-Transform-Equalization Cancellation Based on Multi-Stage APFs Achieving 65dB SIC Across 120MHz BW

全双工技术可应对通信系统高频谱利用率的迫切需求,但存在严重的自干扰。为此,李巍研究员、徐鸿涛研究员团队设计了一款基于多域多抽头希尔伯特均衡消除的宽带全双工接收机。基于提出的低噪声/高延时带宽积全通滤波器,消除电路既能实现射频延时又可保持宽带内平坦的频率响应,且有效降低了对接收机噪声的恶化;同时延迟峰值技术拓展了延时带宽,增强了对多径自干扰信号的消除能力。该芯片对120MHz调制信号实现了总计65dB的自干扰消除,而消除电路对0.5-5GHz宽带接收机噪声恶化仅为1.2-2.1dB,核心面积仅为0.5mm2。该性能在目前国际上已报道的全双工接收机中处于领先水平。

马星宇博士生报告论文

该工作以“Compact Full-Duplex Receiver with Wideband Multi-Domain Hilbert-Transform-Equalization Cancellation Based on Multi-Stage APFs Achieving 65dB SIC Across 120MHz BW”为题,发表于2025年ISSCC的射频与毫米波无线通信接收机(RF and mm-Wave Wireless Receivers)分会场。该文章第一作者及演讲者为复旦大学马星宇博士研究生,通信作者为复旦大学李巍研究员与徐鸿涛研究员。

06

论文六

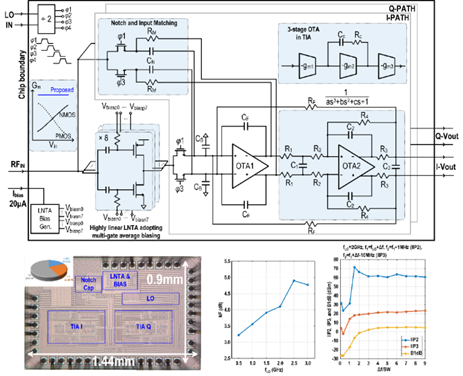

A 200MHz-BW Blocker-Tolerant Receiver with Fifth-Order Filtering Achieving 19dBm Adjacent-Channel IIP3

洪志良教授、黄煜梅教授团队设计的高线性度、低功耗、SAWLESS宽带射频接收机前端芯片,以sub-3GHz 频段、射频带宽200MHz的 SAW-Less 抗阻塞接收前端为研究对象,提出了多栅平均偏置技术用以提升 LNTA 的线性度,且PVT鲁棒性优良,简化了接收机的射频滤波设计同时提升了接收前端的功耗效率;创新地将 Follow-the-Leader-Feedback(FLFB)结构用于跨阻滤波器 TIA 的设计,对 5G 应用场景中的邻带阻塞信号进行有效抑制;提出了高功耗效率的双二阶滤波结构,有效提升了有源 RC 低通滤波器(Low Pass Filter,LPF)的动态范围,并解决了其在 5G 宽带应用中功耗较大的问题。接收前端在 0.5GHz 至 3GHz 的工作频率范围内噪声系数低于 4.9dB,邻带阻塞1dB 压缩点(B1dB)达到-1.2dBm,邻带 IIP3 为 +19dBm;当阻塞信号频偏 600MHz 且功率为 0dBm 时,噪声系数为 10.3dB。该论文发表于RF and mm-Wave Wireless Receivers分会场,并入选ISSCC 2025亮点论文。

射频接收机芯片架构、照片和主要测试结果

该工作以“A 200MHz-BW Blocker-Tolerant Receiver with Fifth-Order Filtering Achieving 19dBm Adjacent-Channel IIP3”为题,发表于2025年IEEE ISSCC 2025。该文章由黄煜梅教授和洪志良教授作为指导老师,第一作者为雷良波博士研究生,并由陈燕翔、李怡杰等学生协助完成。

雷良波博士生报告论文

07

论文七

A Wideband Replicas-Rejection Digital Transmitter Using Joint-Digital-Analog Interpolation and Filtering in 28nm CMOS

数字化射频架构具有低功耗、小面积、高效率且工艺兼容性强等优势,但数字采样会引入带外杂散等问题,从而对其他通讯设备造成干扰。殷韵教授、徐鸿涛研究员团队提出一种“数字-模拟”联合插值滤波的新架构:在数字域提出新型多相插值结构,保证高倍插值同时,实现带外滤波并降低功耗;同时,在模拟域通过延时叠加方法,实现一阶线性插值,进一步抑制镜像信号;为了对宽带镜像信号进行抑制,还引入模拟域滤波器到数字域实现,同时与数字域电路进行有效的合并简化。该芯片核心面积0.88mm2,数字电路功耗仅占系统5%以下,最大系统效率超30%。3dB射频带宽覆盖2.1-5.1GHz,首次实现宽带信号的带外镜像抑制度超42dBc。

胡春晓博士生报告论文

该工作以“A Wideband Replicas-Rejection Digital Transmitter Using Joint-Digital-Analog Interpolation and Filtering in 28nm CMOS”为题,发表于2025年ISSCC的无线发射机和射频前端(Wireless Transmitters and Front-Ends)分会场。该文章第一作者及演讲者为胡春晓博士研究生,通讯作者为殷韵教授和徐鸿涛研究员。